Optical Interconnection Design Innovator

# GIGALIGHT 400G QSFP-DD DR4 500m Silicon Photonics Transceiver Module

P/N: GQD-SI401DR4C

#### **Features**

- ✓ QSFP-DD MSA and CMIS compliant

- ✓ Compliant to 802.3bs 400GBASE-DR4

- √ 8x53.125Gbit/s PAM4 electrical interface(400GAUI-8)

- ✓ 4x106.25Gbps(53.125GBd PAM4)Optics architecture

- √ Power consumption <10W

</p>

- ✓ Maximum link length of 500m G.652 SMF with KP-FEC

- ✓ MPO-12 receptacles

- ✓ Built-in digital diagnostic functions

- ✓ Operating case temperature 0°C to +70°C

- √ 3.3V power supply voltage

- √ RoHS compliant(lead free)

### **Applications**

- ✓ IEEE 802.3bs 400GBASE-DR4

- ✓ Data center network

#### **Description**

The Gigalight GQD-SI401DR4C is a transceiver module designed for 500m optical communication applications, and it is compliant to QSFP-DD MSA, IEEE 802.3bs protocol and 400GAUI-8 standards. The silicon photonics transceiver is based on a new state-of-the-art silicon photonics (SiPh) platform. It uses SiPh chips that integrate a number of active and passive optoelectronic components, 3D packaging technology and industry-leading 7nm DSP chips. It is a cost-effective and lower power consumption solution for 400GBASE data center. It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference. The module offers very high functionality and feature integration, accessible via a two-wire serial interface.

Figure 1. Module Block Diagram

## **Absolute Maximum Ratings**

| Parameter                  | Symbol | Min  | Max     | Unit         |

|----------------------------|--------|------|---------|--------------|

| Supply Voltage             | Vcc    | -0.3 | 3.6     | V            |

| Input Voltage              | Vin    | -0.3 | Vcc+0.3 | V            |

| Storage Temperature        | Tst    | -40  | 85      | $^{\circ}$   |

| Case Operating Temperature | Тор    | 0    | 70      | $^{\circ}$ C |

| Humidity(non-condensing)   | Rh     | 5    | 95      | %            |

## **Recommended Operating Conditions**

| Parameter                  | Symbol | Min  | Typical | Max  | Unit       |

|----------------------------|--------|------|---------|------|------------|

| Supply Voltage             | Vcc    | 3.13 | 3.3     | 3.47 | V          |

| Operating Case temperature | Tca    | 0    |         | 70   | $^{\circ}$ |

| Data Rate Per Lane         | fd     |      | 106.25  |      | Gbit/s     |

| Humidity                   | Rh     | 5    |         | 85   | %          |

| Power Dissipation          | Pm     |      |         | 10   | W          |

Optical Interconnection Design Innovator

www.gigalight.com

## **Electrical Specifications**

| Parameter                               | Symbol | Min   | Typical | Max    | Unit  |

|-----------------------------------------|--------|-------|---------|--------|-------|

| Differential input impedance            | Zin    | 90    | 100     | 110    | ohm   |

| Differential Output impedance           | Zout   | 90    | 100     | 110    | ohm   |

| Differential input voltage amplitude    | ΔVin   | 900   |         |        | mVp-p |

| Differential output voltage amplitude   | ΔVout  |       |         | 900    | mVp-p |

| Bit Error Rate                          | BER    |       |         | 2.4E-4 | -     |

| Near-end ESMW (Eye symmetry mask width) |        | 0.265 |         |        | UI    |

| Near-end Eye height, differential (min) |        | 70    |         |        | mV    |

| Far-end ESMW (Eye symmetry mask width)  |        | 0.20  |         |        | UI    |

| Far-end Eye height, differential (min)  |        | 30    |         |        | mV    |

| Far-end pre-cursor ISI ratio            |        | -4.5  |         | 2.5    | %     |

#### Note:

- BER=2.4E-4; PRBS31Q@26.5625GBd. Pre-FEC

- Differential input voltage amplitude is measured between TxnP and TxnN. 2)

- Differential output voltage amplitude is measured between RxnP and RxnN. 3)

## **Optical Characteristics**

**Table 3 - Optical Characteristics**

| Parameter                                                         | Symbol | Min    | Typical | Max    | Unit | Notes |

|-------------------------------------------------------------------|--------|--------|---------|--------|------|-------|

| Transmitter                                                       |        |        |         |        |      |       |

| Centre Wavelength                                                 | λc     | 1304.5 |         | 1317.5 | nm   | -     |

| Side-mode suppression ratio                                       | SMSR   | 30     | -       |        | dB   | -     |

| Average launch power, each lane                                   | Pout   | -2.9   | -       | 4.0    | dBm  | -     |

| Optical Modulation<br>Amplitude(OMA outer),<br>each lane          | OMA    | -0.8   | -       | 4.2    | dBm  | -     |

| Transmitter and dispersion eye closure for PAM4 (TDECQ),each lane | TDECQ  |        |         | 3.4    | dB   |       |

| www.gigalight.com                                      |       |         |   | Optical Inte | rconnectio | n Design Innova |

|--------------------------------------------------------|-------|---------|---|--------------|------------|-----------------|

| Extinction Ratio                                       | ER    | 3.5     | - | -            | dB         | -               |

| Average launch power of OFF transmitter, each lane     |       |         |   | -15          | dB         | -               |

|                                                        |       | Receive | r |              |            |                 |

| Centre Wavelength                                      | λc    | 1304.5  |   | 1317.5       | nm         | -               |

| Receiver Sensitivity in OMA outer                      | RXsen |         |   | -4.4         | dBm        | 1               |

| Average power at receiver , each lane input, each lane | Pin   | -5.9    |   | 4            | dBm        | -               |

| Receiver Reflectance                                   |       |         |   | -26          | dB         | -               |

| LOS Assert                                             |       | -12     |   |              | dBm        | -               |

| LOS De-Assert                                          |       |         |   | -10          | dBm        | -               |

| LOS Hysteresis                                         |       | 0.5     |   |              | dB         | -               |

#### Note:

1) Measured with conformance test signal at TP3 for BER = 2.4E-4 Pre-FEC

## **Pin Description**

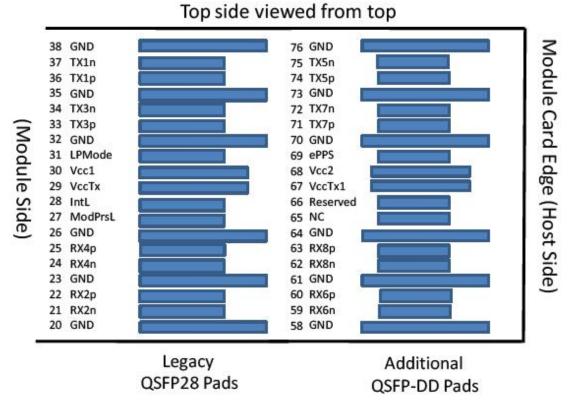

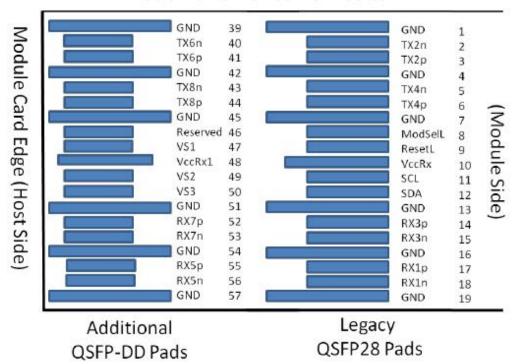

## Table 1- Pad Function Definition

| Pad  | Logic                                   | Symbol  | Description                         | Plug<br>Sequence <sup>4</sup> | Notes |

|------|-----------------------------------------|---------|-------------------------------------|-------------------------------|-------|

| 1    |                                         | GND     | Ground                              | 1B                            | 1     |

| 2    | CML-I                                   | Tx2n    | Transmitter Inverted Data Input     | 3B                            |       |

| 3    | CML-I                                   | Tx2p    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 4    | 100000000000000000000000000000000000000 | GND     | Ground                              | 1B                            | 1     |

| 5    | CML-I                                   | Tx4n    | Transmitter Inverted Data Input     | 3B                            |       |

| 6    | CML-I                                   | Tx4p    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 7    | 1000200100000                           | GND     | Ground                              | 1B                            | 1     |

| 8    | LVTTL-I                                 | ModSelL | Module Select                       | 3B                            |       |

| 9    | LVTTL-I                                 | ResetL  | Module Reset                        | 3B                            |       |

| 10   |                                         | VccRx   | +3.3V Power Supply Receiver         | 2B                            | 2     |

| 11   | LVCMOS-<br>I/O                          | SCL     | 2-wire serial interface clock       | 3B                            |       |

| 12   | LVCMOS-<br>I/O                          | SDA     | 2-wire serial interface data        | 3B                            |       |

| 13   |                                         | GND     | Ground                              | 1B                            | 1     |

| 14   | CML-O                                   | Rx3p    | Receiver Non-Inverted Data Output   | 3B                            | -55   |

| 15   | CML-O                                   | Rx3n    | Receiver Inverted Data Output       | 3B                            |       |

| 16   |                                         | GND     | Ground                              | 1B                            | 1     |

| 17   | CML-O                                   | Rx1p    | Receiver Non-Inverted Data Output   | 3B                            |       |

| 18   | CML-O                                   | Rx1n    | Receiver Inverted Data Output       | 3B                            | - 500 |

| 19   |                                         | GND     | Ground                              | 1B                            | 1     |

| 20   |                                         | GND     | Ground                              | 1B                            | 1     |

| 21   | CML-0                                   | Rx2n    | Receiver Inverted Data Output       | 3B                            |       |

| 22   | CML-0                                   | Rx2p    | Receiver Non-Inverted Data Output   | 3B                            |       |

| 23   |                                         | GND     | Ground                              | 1B                            | 1     |

| 24   | CML-O                                   | Rx4n    | Receiver Inverted Data Output       | 3B                            |       |

| 25   | CML-O                                   | Rx4p    | Receiver Non-Inverted Data Output   | 3B                            |       |

| 26   |                                         | GND     | Ground                              | 1B                            | 1     |

| 27   | LVTTL-0                                 | ModPrsL | Module Present                      | 3B                            |       |

| 28   | LVTTL-0                                 | IntL    | Interrupt                           | 3B                            |       |

| 29   |                                         | VccTx   | +3.3V Power supply transmitter      | 2B                            | 2     |

| 30   |                                         | Vcc1    | +3.3V Power supply                  | 2B                            | 2     |

| 31   | LVTTL-I                                 | LPMode  | Low Power mode;                     | 3B                            |       |

| 32   |                                         | GND     | Ground                              | 1B                            | 1     |

| 33   | CML-I                                   | Tx3p    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 34   | CML-I                                   | Tx3n    | Transmitter Inverted Data Input     | 3B                            |       |

| 35   |                                         | GND     | Ground                              | 1B                            | 1     |

| 36   | CML-I                                   | Tx1p    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 37   | CML-I                                   | Tx1n    | Transmitter Inverted Data Input     | 3B                            |       |

| 2.12 |                                         | GND     | Ground                              | 1B                            | 1     |

Optical Interconnection Design Innovator

| Pad | Logic   | Symbol   | Description                                         | Plug<br>Sequence <sup>4</sup> | Notes |

|-----|---------|----------|-----------------------------------------------------|-------------------------------|-------|

| 39  |         | GND      | Ground                                              | 1A                            | 1     |

| 40  | CML-I   | Tx6n     | Transmitter Inverted Data Input                     | 3A                            |       |

| 41  | CML-I   | Tx6p     | Transmitter Non-Inverted Data Input                 | 3A                            |       |

| 42  |         | GND      | Ground                                              | 1A                            | 1     |

| 43  | CML-I   | Tx8n     | Transmitter Inverted Data Input                     | 3A                            |       |

| 44  | CML-I   | Tx8p     | Transmitter Non-Inverted Data Input                 | 3A                            |       |

| 45  | 1       | GND      | Ground                                              | 1A                            | 1     |

| 46  |         | Reserved | For future use                                      | 3A                            | 3     |

| 47  |         | VS1      | Module Vendor Specific 1                            | 3A                            | 3     |

| 48  |         | VccRxl   | 3.3V Power Supply                                   | 2A                            | 2     |

| 49  |         | VS2      | Module Vendor Specific 2                            | 3A                            | 3     |

| 50  | ĺ.      | VS3      | Module Vendor Specific 3                            | 3A                            | 3     |

| 51  | 1       | GND      | Ground                                              | 1A                            | 1     |

| 52  | CML-O   | Rx7p     | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 53  | CML-O   | Rx7n     | Receiver Inverted Data Output                       | 3A                            |       |

| 54  |         | GND      | Ground                                              | 1A                            | 1     |

| 55  | CML-O   | Rx5p     | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 56  | CML-O   | Rx5n     | Receiver Inverted Data Output                       | 3A                            |       |

| 57  |         | GND      | Ground                                              | 1A                            | 1     |

| 58  |         | GND      | Ground                                              | 1A                            | 1     |

| 59  | CML-O   | Rx6n     | Receiver Inverted Data Output                       | 3A                            |       |

| 60  | CML-O   | Rx6p     | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 61  |         | GND      | Ground                                              | 1A                            | 1     |

| 62  | CML-O   | Rx8n     | Receiver Inverted Data Output                       | 3A                            |       |

| 63  | CML-O   | Rx8p     | Receiver Non-Inverted Data Output                   | 3A                            |       |

| 64  |         | GND      | Ground                                              | 1A                            | 1     |

| 65  |         | NC       | No Connect                                          | 3A                            | 3     |

| 66  |         | Reserved | For future use                                      | 3A                            | 3     |

| 67  |         | VccTxl   | 3.3V Power Supply                                   | 2A                            | 2     |

| 68  |         | Vcc2     | 3.3V Power Supply                                   | 2A                            | 2     |

| 69  | LVTTL-I | ePPS     | Precision Time Protocol (PTP) reference clock input | 3A                            | 3     |

| 70  |         | GND      | Ground                                              | 1A                            | 1     |

| 71  | CML-I   | Tx7p     | Transmitter Non-Inverted Data Input                 | 3A                            |       |

| 72  | CML-I   | Tx7n     | Transmitter Inverted Data Input                     | 3A                            |       |

| 73  | (1)     | GND      | Ground                                              | 1A                            | 1     |

| 74  | CML-I   | Tx5p     | Transmitter Non-Inverted Data Input                 | 3A                            |       |

| 75  | CML-I   | Tx5n     | Transmitter Inverted Data Input                     | 3A                            |       |

| 76  |         | GND      | Ground                                              | 1A                            | 1     |

Note 1: QSFP-DD uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

Note 2: VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the host side of the Host Card Edge Connector are listed in Table 7. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The connector Vcc pins are each rated for a maximum current of 1000 mA.

Note 3: All Vendor Specific, Reserved, No Connect and ePPS (if not used) pins may be terminated with 50 Ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF.

Note 4: Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A,1B will then occur simultaneously, followed by 2A,2B,followed by 3A,3B.

## Bottom side viewed from bottom

Figure 2. Electrical Pin-out Details

#### ModSelL Pin

The ModSelL is an input signal that shall be pulled to Vcc in the QSFP-DD module. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP-DD modules on a single 2-wire interface bus. When ModSelL is "High", the module shall not respond to or acknowledge any 2-wire interface communication from the host. In order to avoid conflicts, the host system shall not attempt 2-wire interface communications within the ModSelL de-assert time after any QSFP-DD modules are deselected. Similarly, the host must wait at least for the period of the ModSelL assert time before communicating with the newly selected module. The assertion and de-asserting periods of different modules may overlap as long as the above timing requirements are met.

#### ResetL Pin

The ResetL signal shall be pulled to Vcc in the module. A low level on the ResetL signal for longer than the minimum pulse length (t\_Reset\_init) initiates a complete module reset, returning all user module settings to their default state.

#### LPMode Pin

LPMode is an input signal. The LPMode signal shall be pulled up to Vcc in the QSFP-DD module. LPMode is used in the control of the module power mode. See CMIS Section 6.3.1.3.

#### ModPrsL Pin

ModPrsL shall be pulled up to Vcc Host on the host board and pulled low in the module. The ModPrsL is asserted "Low" when the module is inserted. The ModPrsL is deasserted "High" when the module is physically absent from the host connector due to the pull-up resistor on the host board.

#### IntL Pin

IntL is an output signal. The IntL signal is an open collector output and shall be pulled to Vcc Host on the host board. When the IntL signal is asserted Low it indicates a change in module state, a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt using the 2-wire serial interface. The IntL signal is deasserted "High" after all set interrupt flags are read.

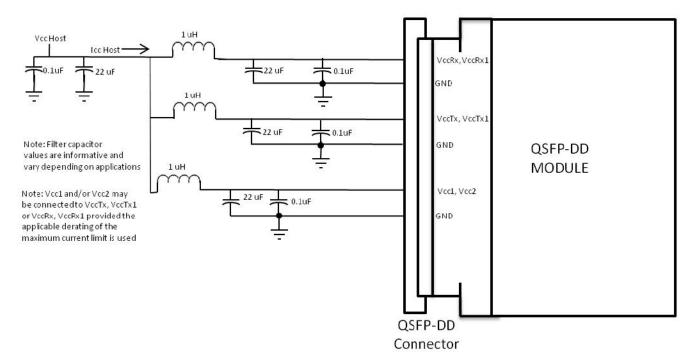

# **Power Supply Filtering**

The host board should use the power supply filtering shown in Figure 3.

Figure 3. Host Board Power Supply Filtering

#### DIAGNOSTIC MONITORING INTERFACE

Digital diagnostics monitoring function is available on all Gigalight QSFP DD products. A 2-wire serial interface provides user to contact with module.

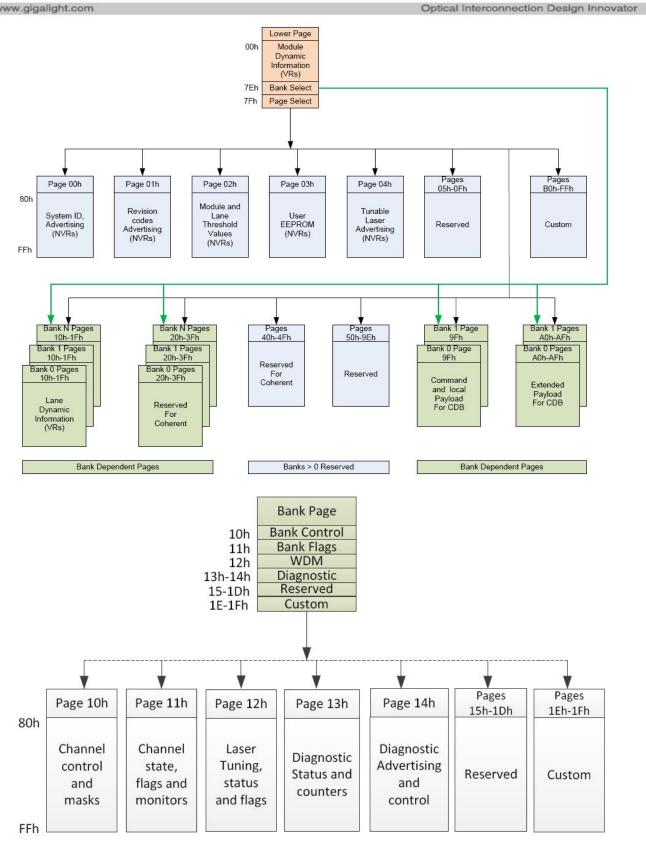

#### **Memory Structure and Mapping**

This limits the management memory that can be directly accessed by the host to 256 bytes, which is divided in Lower Memory (addresses 00h through 7Fh) and Upper Memory (addresses 80h through FFh).

A larger addressable management memory is required for all but the most basic modules. This is supported by a structure of 128-byte pages, together with a mechanism for dynamically mapping any of the 128-byte pages from a larger internal management memory space into Upper Memory the host addressable space.

The addressing structure of the additional internal management memory2 is shown in Figure 4 The management memory inside the module is arranged as a unique and always host accessible address space of 128 bytes (Lower Memory) and as multiple upper address subspaces of 128 bytes each

www.gigalight.com Optical Interconnection Design Innovator

(Pages), only one of which is selected as host visible in Upper Memory. A second level of Page selection is possible for Pages for which several instances exist (e.g. where a bank of pages with the same Page number exists).

This structure supports a flat 256 byte memory for passive copper modules and permits timely access to addresses in the Lower Memory, e.g. Flags and Monitors. Less time critical entries, e.g. serial ID information and threshold settings, are available with the Page Select function in the Lower Page. For more complex modules which require a larger amount of management memory the host needs to use dynamic mapping of the various Pages into the host addressable Upper Memory address space, whenever needed.

**Note**: The management memory map has been designed largely after the QSFP memory map. This memory map has been changed in order to accommodate 8 electrical lanes and to limit the required memory space. The single address approach is used as found in QSFP. Paging is used in order to enable time critical interactions between host and module.

#### **Supported Pages**

A basic 256 byte subset of the Management Memory Map is mandatory for all CMIS compliant devices. Other parts are only available for paged memory modules, or when advertised by the module. See CMIS V4.0 for details regarding the advertisement of supported management memory spaces.

In particular, support of the Lower Memory and of Page 00h is required for all modules, including passive copper cables. These pages are therefore always implemented. Additional support for Pages 01h, 02h and bank 0 of Pages 10h and 11h is required for all paged memory modules.

Bank 0 of pages 10h-1Fh, provides lane-specific registers for the first 8 lanes, and each additional bank provides support for additional 8 lanes. Note, however, that the allocation of information over the banks may be page specific and may not to be related to grouping data for 8 lanes.

The structure allows address space expansion for certain types of modules by allocating additional Pages. Moreover, additional banks of pages.

Gigalight

Figure 4. QSFP DD Memory Map

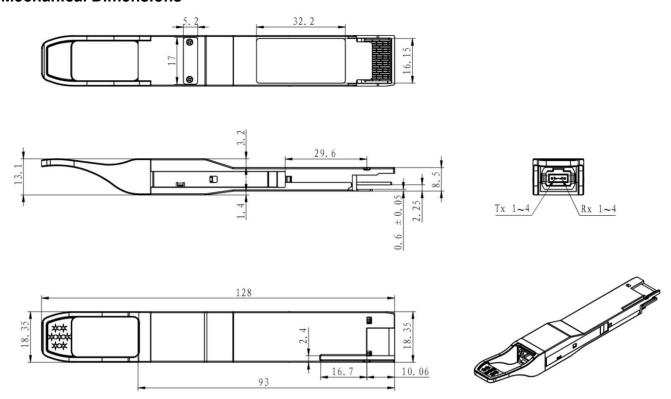

#### **Mechanical Dimensions**

Figure 5. Mechanical Specifications

## **Regulatory Compliance**

Gigalight GQD-SI401DR4C transceivers are Class 1 Laser Products. They meet the requirements of the following standards:

| Feature                  | Standard                                                                                                             |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|

| Laser Safety             | IEC 60825-1:2014 (3 <sup>rd</sup> Edition)<br>IEC 60825-2:2004/AMD2:2010<br>EN 60825-1-2014<br>EN 60825-2:2004+A1+A2 |

| Electrical Safety        | EN 62368-1: 2014<br>IEC 62368-1:2014<br>UL 62368-1:2014                                                              |

| Environmental protection | Directive 2011/65/EU with amendment(EU)2015/863                                                                      |

| CE EMC                   | EN55032: 2015<br>EN55035: 2017<br>EN61000-3-2:2014<br>EN61000-3-3:2013                                               |

| ************************************** |

|----------------------------------------|

| Gigalight                              |

| 0.342.3                                |

Optical Interconnection Design Innovator

| FCC | FCC Part 15, Subpart B<br>ANSI C63.4-2014 |

|-----|-------------------------------------------|

#### References

- QSFP-DD MSA

- 2. CMIS

- IEEE802.3bs 400GBASE-DR4

- 4. OIF CEI-56G-VSR-PAM4

# **ACAUTION:**

Use of controls or adjustment or performance of procedures other than those specified herein may result in hazardous radiation exposure.

#### Ordering information

| Part Number   | Product Description                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------|

| GQD-SI401DR4C | QSFP DD, 400GBASE-DR4, 500m on Single mode Fiber (SMF),with DSP Power consumption <10W, MPO-12 connector. |

#### **Important Notice**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by GIGALIGHT before they become applicable to any particular order or contract. In accordance with the GIGALIGHT policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of GIGALIGHT or others. Further details are available from any GIGALIGHT sales representative.

E-mail: sales@gigalight.com Official Site: www.gigalight.com

#### **Revision History**

| Revision | Date        | Description      |

|----------|-------------|------------------|

| V0       | Aug-29-2022 | Advance Release. |

#### 深圳市易飞扬通信技术有限公司 Shenzhen Gigalight Technology Co., Ltd.

V1 Oct-16-2023 Updated structure pull ring color